S & M 2933

# Electrostatic Discharge Reliability Sensing of Ultrahigh-voltage N-channel Laterally Diffused MOSFETs Modulated by Different Operating Voltages

Jhong-Yi Lai,<sup>1</sup> Shen-Li Chen,<sup>1\*</sup> Zhi-Wei Liu,<sup>1</sup> Hung-Wei Chen,<sup>1</sup> Hsun-Hsiang Chen,<sup>2</sup> and Yi-Mu Lee<sup>1</sup>

<sup>1</sup>Department of Electronic Engineering, National United University, No. 2, Lienda, Miaoli 360302, Taiwan <sup>2</sup>Department of Electronic Engineering, National Changhua University of Education, Changhua, Taiwan

(Received December 2, 2021; accepted March 28, 2022)

*Keywords:* bipolar-CMOS-DMOS (BCD), device under test (DUT), electrostatic discharge (ESD), holding voltage ( $V_h$ ), laterally diffused MOSFET (LDMOS), optical microscopy (OM), secondary breakdown current ( $I_{t2}$ ), transmission-line pulse (TLP), trigger voltage ( $V_{t1}$ ), ultrahigh voltage (UHV)

In this paper, electrostatic discharge (ESD) reliability sensing components for use in ultrahigh- to low-voltage environments were fabricated via a Taiwan Semiconductor Manufacturing Company (TSMC) 0.5  $\mu$ m ultrahigh voltage (UHV) bipolar-CMOS-DMOS (BCD) process. To understand the trend of the capability of different voltage components under ESD stress, we designed ESD sensing components that can be used at different voltages. These ESD sensing components will be implemented using a circular layout. By changing the drift region and Poly2 parameters with a fixed gate terminal, we proposed a new design with eight sets of parameters. As the length of the drain-side drift region ( $L_D$ ) increases, the parasitic resistance of the drift region also increases, which will improve the ability of the device to withstand ESD currents. Eventually, to further analyze the ESD capability of the component, a transmission-line pulse (TLP) test system was used for the DUT. When  $L_D$  is 28  $\mu$ m, the device is optimal. The  $I_{t2}$  of the device can reach 4.43 A. The FOM is also used to determine the ESD capability of the component, which can reach a maximum of  $3.15 \times 10^2$  (A·V/ $\mu$ m<sup>2</sup>).

## 1. Introduction

With the development of semiconductor technology and the advancement of component processes, the area of commercial ICs has continually decreased. However, as the component area decreases, it is likely to cause more and more electrostatic discharge (ESD) damage events and partial circuit failures. In addition, ESD events can often easily cause internal damage to IC devices.<sup>(1-5)</sup> ESD failures of components are usually more severe at higher operating voltages. However, because the ESD energy is not very high, it is often difficult to detect ESD damage by optical microscopy (OM) especially for low operating voltages.<sup>(6-9)</sup> Therefore, high-voltage or ultrahigh-voltage (UHV) ESD protection designs must be applied in many power management circuits such as AC/DC converter circuits, automotive electronics, and liquid crystal displays

\*Corresponding author: e-mail: jackchen@nuu.edu.tw https://doi.org/10.18494/SAM3768 (LCDs). To prevent ESD events from increasing the damage to components, we use TSMC 0.5  $\mu$ m UHV process components for self-protection component designs in this study.<sup>(9–16)</sup> These UHV devices will be presented in a circular layout, and the final optimal design is expected to have high/ultrahigh-voltage components with different breakdown voltages and an excellent ESD capability in ESD sensing applications. It is hoped that the final designed components can be used as protection components under different operating voltages, and the ESD capability of these components is analyzed through TLP measurements.<sup>(17–25)</sup>

## 2. Device Structures

### 2.1 UHV n-channel laterally diffused MOSFET (nLDMOS) reference device

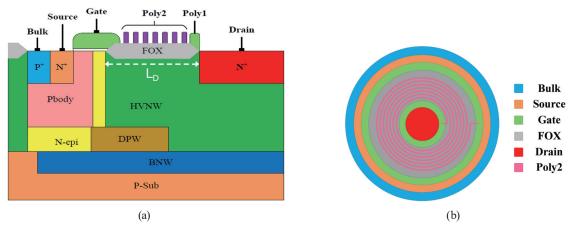

Figures 1(a) and 1(b) show the structure of the reference device for our design. To protect the IC I/O circuit, a gate-to-ground NMOS (GGNMOS) design was adopted for test purposes. Owing to the GGNMOS architecture, this MOSFET will not trigger conduction under normal conditions. However, this component is instead conducted by a parasitic bipolar junction transistor (BJT) path as in an EOS situation. Then, an UHV nLDMOS components is designed in a circular layout. The Poly2 layer is used to increase the breakdown voltage (and operating voltage) of the components, and it is designed to be spiral. The overall length of the Poly2 layer is easily increased by the spiral layout. Then, the drift region creates a large field-plate effect, which leads to an increase in breakdown voltage, which allows these devices to operate in UHV environments. Because the Poly2 layer is related to the floating condition, it reduces the on-state field. The buried N-well (BNW) layer is highly doped on top of P-sub, and its purpose is to form a reverse diode with P-sub to prevent the excessive leakage current from flowing to the P-sub region. The deep P-well (DPW) layer is also designed with a high-voltage N-well (HVNW) inside the component to form a RESURF, which increases the breakdown voltage of the component. The length of the drift region  $(L_D)$  is defined as the distance between the HVNW and the drain terminal N<sup>+</sup>, and is also the main subject of this work.

Fig. 1. (Color online) (a) Cross section and (b) layout view of the UHV nLDMOS reference component.

## 2.2 Design devices for different operating voltages

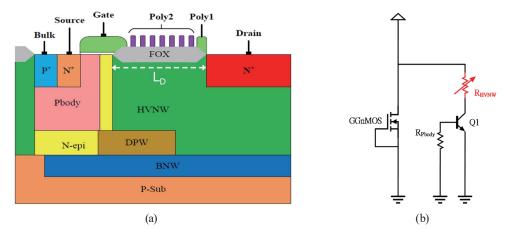

To use the components in different operating voltage ranges, a reference device of components is used to adjust the component parameters. The component breakdown voltages are designed to be in the ranges of 100 to 200 V, 200 to 300 V, and above 300 V. As shown in Fig. 2(a), the breakdown voltage is adjusted by changing  $L_D$  and the number of turns of Poly2 (N<sub>P</sub>). As  $L_D$ determines the size of the HVNW, the parasitic resistance  $(R_{HVNW})$  on the HVNW will also be proportional to the HVNW zone in Fig. 2(b). As the length of the HVNW increases, the larger parasitic resistance due to the longer distance across the component causes the current density to decrease, and hence the ESD current flow is improved. To maintain the breakdown voltage in the operating voltage range,  $L_D$  is strongly related to the breakdown voltage. The drift region parameters are then designed according to the default voltage. As  $L_D$  decreases, this Poly2 reduces the number of turns in the drift region. The device modulation parameters are shown in Table 1. However, when the parameter of the drift region is less than 15  $\mu$ m (S15 R), the Poly1 and metal layer parameters are considered to be the same. This results in the new device not having a Poly2 layer layout, which causes the loss of the field plate effect above the field oxide (FOX). This will cause the breakdown voltage to drop quickly and alter the linear relationship of the falling breakdown voltage.

Fig. 2. (Color online) (a) Cross-sectional view of UHV nLDMOS components and (b) equivalent circuit.

| Layer parameters of | parameters of UHV nLDMOS components.time $N_p$ (turn) $L_D$ (µm) |    |  |  |  |

|---------------------|------------------------------------------------------------------|----|--|--|--|

| Cell name           | $N_p$ (turn) $L_D$ (µm                                           |    |  |  |  |

| S13_R               | 0                                                                | 13 |  |  |  |

| S14_R               | 0                                                                | 14 |  |  |  |

| S15_R               | 0                                                                | 15 |  |  |  |

| S18_R               | 1                                                                | 18 |  |  |  |

| S21_R               | 3                                                                | 21 |  |  |  |

| S24_R               | 5                                                                | 24 |  |  |  |

| S27_R               | 6                                                                | 27 |  |  |  |

| S28_R               | 7                                                                | 28 |  |  |  |

Table 1 Layer parameters of UHV nLDMOS components.

Thus far, it has been found that if  $L_D$  is large, the  $I_{l2}$  capability of the device is effective. However, the component area increases and the chip cost is also higher. Therefore, the design factor of merit (FOM) can be used to analyze component capabilities and determine which component is better. The FOM can be determined as

$$FOM = V_h(V) \times I_{t2}(A) / Cell Area (\mu m^2),$$

(1)

where  $V_h$  is the holding voltage. This value is related to the ability to withstand the latch-up immunity.  $I_{t2}$  is the maximum secondary breakdown current that a component can withstand. By multiplying these two values, the reliability of the component can be more accurately determined by the ESD/latch-up capability of the design.

# 3. Test Machines

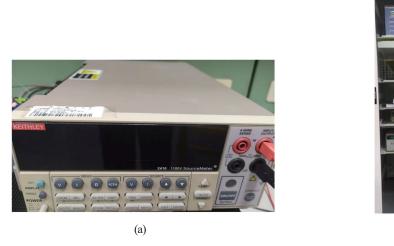

First, it is necessary to know whether the operating voltage of the component is within the voltage range. We used the breakdown voltage to determine it. Here, a Keithley-2410 tester was used to measure the breakdown voltage (i.e., operating voltage) of devices as shown in Fig. 3(a). The DC breakdown voltage is measured by limiting the component leakage current. The breakdown voltage point is defined as the voltage when the leakage current of a device reaches 1  $\mu$ A.

Next, a TLP system was used to analyze the ESD capability of the devices as shown in Fig. 3(b). ESD events quickly occur and the damage to the component is very significant. In other words, the TLP system is used to simulate the real human body model (HBM). The TLP system uses a fast square wave to zap the component. The rising and falling time of the square wave is approximately 10 ns and the pulse width is about 100 ns. The initial voltage of the device is 5 V, and the bombardment voltage rises by 1 V after each test. A component leakage current of greater than 1  $\mu$ A indicates that the component has already failed. At this moment, the TLP will stop the ESD test.

Fig. 3. (Color online) (a) Keithley-2410 and (b) TLP systems.

(b)

## 4. Test Results and Discussion

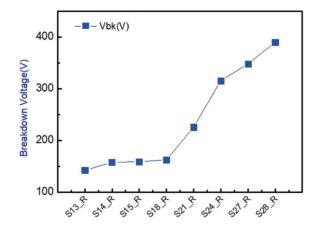

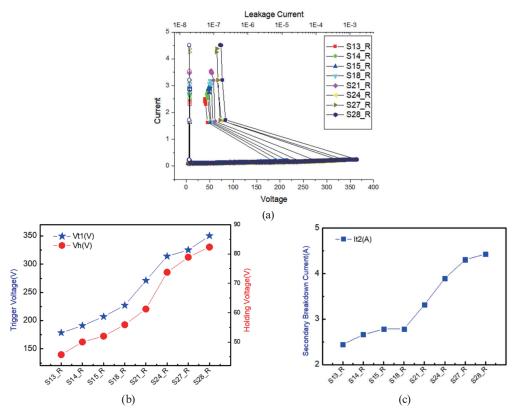

The test starts with the measurement of the breakdown voltage. As can be seen from Fig. 4, there are four types of device with breakdown voltages between 100 and 200 V, the other group is between 200 and 300 V, and the third group is above 300 V. Although there are some differences from the original design, it can be seen that the breakdown voltage increases with  $L_D$ . At 15 µm (S15\_R), the absence of Poly2 causes the breakdown voltage to change at a rate that is not linear in relation to the HVNW change as expected. It can also be seen from the figure that the breakdown voltage of the drift-region design of the 18 µm (S18\_R) sample is not markedly different from that of the 15 µm one. This is probably due to the fact that Poly2 is designed as a single turn, so the total area of Poly2 is insufficient to generate the field plate effect. This resulted in no significant increase in the breakdown voltage of the component. This phenomenon indicates that the field plate effect is very important to the breakdown voltage variation.

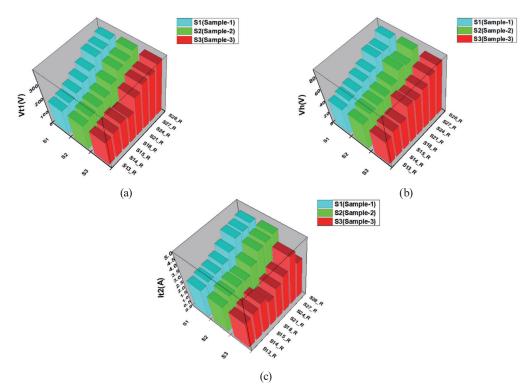

Then, to further analyze the ESD/latch-up capability, we used a TLP tester to measure these samples. To reduce the production and measurement errors, we measured the data of three different samples as shown in Fig. 5, which will eventually be averaged.

The test averages are arranged in Fig. 6, and the TLP IV-snapback results are shown in Fig. 6(a), where  $V_{t1}$  is the maximum triggering voltage of the parasitic BJT component and  $V_h$  is the minimum on-state voltage of the BJT.  $I_{t2}$  is the maximum current that the component can withstand. The trends of component  $V_{t1}-V_h$  are shown in Fig. 6(b). As  $R_{HVNW}$  [shown in Fig. 2(b)] increases, the parasitic BJT  $V_{t1}$  increases as the breakdown voltage of the component increases owing to the high resistance. When  $R_{HVNW}$  continues to increase, the corresponding  $V_{t1}$  and  $V_h$  of this device will also increase with it. As shown in Fig. 6(c), the increase in  $R_{HVNW}$  leads to a higher  $I_{t2}$  value owing to the relative increase in current that the device can withstand. The  $I_{t2}$  trend shows a positive relationship with  $L_D$ . Finally, the measured component breakdown voltage and TLP parameters are shown in Table 2. The FOM data in the table show that when  $L_D$  is 28 µm (S28\_R), it has better  $I_{t2}$  reliability characteristics than the other devices.

Fig. 4. (Color online) Breakdown voltage test results.

Fig. 5. (Color online) (a)  $V_{t1}$ , (b)  $V_h$ , and (c)  $I_{t2}$  data distributions of TLP test of three different samples.

Fig. 6. (Color online) (a) TLP snapback curves, (b)  $V_{t1}-V_h$  trend plots, and (c)  $I_{t2}$  trend plot of UHV nLDMOS-related components.

| Cell name | $V_{t1}$ (V) | $V_{h}(\mathbf{V})$ | $I_{t2}(\mathbf{A})$ | $FOM_{TLP}$<br>(V·A/ $\mu$ m <sup>2</sup> ) | $V_{bk}\left(\mathbf{V}\right)$ |

|-----------|--------------|---------------------|----------------------|---------------------------------------------|---------------------------------|

| S13 R     | 178.39       | 45.77               | 2.44                 | $1.70 \times 10^2$                          | 142.71                          |

| S14 R     | 191.05       | 50.09               | 2.66                 | $1.94 \times 10^{2}$                        | 158.13                          |

| S15 R     | 207.00       | 52.05               | 2.78                 | $2.02 \times 10^{2}$                        | 159.41                          |

| S18 R     | 227.11       | 55.94               | 2.78                 | $1.92 \times 10^{2}$                        | 162.72                          |

| S21 R     | 271.06       | 61.29               | 3.31                 | $2.24 \times 10^{2}$                        | 226.05                          |

| S24 R     | 314.00       | 73.81               | 3.89                 | $2.84 \times 10^{2}$                        | 315.87                          |

| S27 R     | 325.08       | 78.93               | 4.30                 | $3.03 \times 10^{2}$                        | 348.45                          |

| S28_R     | 350.28       | 82.37               | 4.43                 | $3.15 \times 10^{2}$                        | 389.91                          |

Table 2

Breakdown voltage and TLP test results of UHV nLDMOS-related components.

# 5. Conclusions

In this paper, we focused on the modulation with a fixed gate length using the drift region to change the breakdown voltage (and operating voltage) of the components. This enables a UHV process to be used in the ultrahigh-, high-, and low-voltage ranges. The operating voltage range of a component can be adjusted by changing  $L_D$  of the component. This enables the design of ESD reliability sensors with different operating voltages. This can be seen as a change in the length of the HVNW in the drift region, which will lead to part of the curve close to a linearized high resistance. This is because the parasitic resistance  $R_{HVNW}$  varies with  $L_D$ . Finally, the FOM data show that FOM data are better than the other devices when  $L_D$  is 28 µm (S28\_R). S28\_R also has the highest FOM, where S28\_R has an  $I_{t2}$  of 4.43 A (good ESD immunity). Compared to a device with the lowest breakdown voltage (and operating voltage) and with a drift region of 13 µm (S13\_R), S28\_R has an 173.22% increasing in breakdown voltage and the highest  $V_h$  (with good latch-up capability).

#### Acknowledgments

The authors would like to thank the Taiwan Semiconductor Research Institute for providing the process information and fabrication platform.

## References

- Y. Xiao, A. Concannon, and R. Sankaralingam: Proc. 2015 37th Electrical Overstress/Electrostatic Discharge Symp. (EOS/ESD, 2015) 1–7. <u>https://doi.org/10.1109/EOSESD.2015.7314762</u>

- 2 J. Shao, Y. Qiao, Q. Ma, J. Li, Y. Chen, Y. Yuan, X. Tang, H. Zhang, and D. Zhao: Proc. 2017 18th Int. Conf. Electronic Packaging Technology (ICEPT, 2017) 69–71. <u>https://doi.org/10.1109/ICEPT.2017.8046409</u>

- 3 R. Ye, S. Liu, Z. Dai, H. Chen, W. Wu, W. Sun, S. Lu, W. Su, F. Lin, and G. Sun: Proc. 2018 IEEE 30th Int. Symp. Power Semiconductor Devices and ICs (IEEE, 2018) 339-342. <u>https://doi.org/10.1109/ ISPSD.2018.8393672</u>

- 4 P. Schrey: Proc. 2018 14th Conf. Ph.D. Research in Microelectronics and Electronics (PRIME, 2018) 93–96. <u>https://doi.org/10.1109/PRIME.2018.8430342</u>

- 5 Y. Wang, X. Jin, Y. Peng, J. Luo, Z. Zhong, and J. Yang: IEEE Access 8 (2020) 217213. <u>https://doi.org/10.1109/</u> <u>ACCESS.2020.3042313</u>

- 6 M. Ker, P. Chiu, W. Shieh, and C. Wang: Proc. 2017 IEEE 24th Int. Symp. Physical and Failure Analysis of Integrated Circuits (IEEE, 2017) 1–5. <u>https://doi.org/10.1109/IPFA.2017.8060061</u>

- 7 T. Hung and M. Ker: Proc. 2017 IEEE 24th Int. Symp. Physical and Failure Analysis of Integrated Circuits (IEEE, 2017) 1–6. <u>https://doi.org/10.1109/IPFA.2017.8060079</u>

- 8 M. Raquibuzzaman, B. Ray, T. B. Boykin, and R. S. Gorur: IEEE Trans. Dielectr. Electr. Insul. 25 (2018) 2375. https://doi.org/10.1109/TDEI.2018.007204

- 9 X. Huang, X. Huang, K. Ding, Y. Song, S. Liu, and J. Li: IEEE Trans. Appl. Supercond. 31 (2021) 1. <u>https://doi.org/10.1109/TASC.2021.3094459</u>

- 10 C. Wu, J. Lee, and C. Lien: IEEE Trans. Electron Devices 62 (2015) 4135. <u>https://doi.org/10.1109/ TED.2015.2493879</u>

- 11 T. C. Kao, C. H. Lien, C. W. Chiu, J. H. Lee, Y. H. Lo, C. Y. Hung, T. Y. Huang, and H. D. Su: Proc. 2015 IEEE Int. Reliability Physics Symp. (IEEE, 2015) EL.5.1–5.5. <u>https://doi.org/10.1109/IRPS.2015.7112796</u>

- 12 S. Kim, D. LaFonteese, D. Zhu, D. S. Sridhar, S. Pendharkar, H. Endoh, and K. Boku: Proc. 2017 29th Int. Symp. Power Semiconductor Devices and IC's (ISPSD, 2017) 467-470. <u>https://doi.org/10.23919/</u> <u>ISPSD.2017.7988880</u>

- 13 L. Lu, R. Ye, S. Liu, and W. Sun: Proc. 2019 IEEE 26th Int. Symp. Physical and Failure Analysis of Integrated Circuits (IEEE, 2019) 1–4. <u>https://doi.org/10.1109/IPFA47161.2019.8984813</u>

- 14 H. Liang, L. Zhu, and X. Gu: IEEE J. Emerging Sel. Top. Power Electron. 9 (2021) 6293. <u>http://ieeexplore.ieee.org/document/9272974</u>

- 15 Z. Zhong and X. Jin: Proc. 2020 Int. EOS/ESD Symp. Design and System (IEDS, 2021) 1–4. <u>https://doi.org/10.23919/IEDS48938.2021.9468862</u>

- 16 N. K. Kranthi, J. D. Sarro, R. Sankaralingam, G. Boselli, and M. Shrivastava: IEEE Trans. Electron Devices 68 (2021) 4242. <u>https://doi.org/10.1109/TED.2021.3100810</u>

- 17 P. Mahajan, S. Suresh, A. Quah, F. Rivai, R. Jain, U. Singh, R. Gauthier, and K. Jin Hw: Proc. 2019 Electron Devices Technology and Manufacturing Conf. (EDTM, 2019) 172–175. <u>https://doi.org/10.1109/ EDTM.2019.8731306</u>

- 18 F. Du, S. Song, F. Hou, W. Song, L. Chen, J. Liu, Z. Liu, and J. J. Liou: IEEE Electron Device Lett. 40 (2019) 1491. <u>https://doi.org/10.1109/LED.2019.2926103</u>

- 19 D. Lai, G. de Raad, S. Sque, W. Peters, and T. Smedes: IEEE Trans. Electron Devices 66 (2019) 2884. <u>https://doi.org/10.1109/TED.2019.2917264</u>

- 20 E. Hossain, S. S. Chowdhury, M. Matin, A. M. Ahmed, and M. M. A. Hakim: Proc. 2020 IEEE Region 10 Symp. (IEEE, 2020) 1164–1167. <u>https://doi.org/10.1109/TENSYMP50017.2020.9230678</u>

- 21 K. Sun, T. Li, and L. Meng: IEEE Trans. Electron Devices 68 (2021) 934. <u>https://doi.org/10.1109/</u> <u>TED.2020.3046162</u>

- 22 Y. Lu, Y. Hong, and Y. Cheng: Proc. 2021 5th IEEE Electron Devices Technology & Manufacturing Conf. (IEEE, 2021) 1–3. <u>https://doi.org/10.1109/EDTM50988.2021.9420937</u>

- 23 P. Mahajan, R. Kumar, R. Gauthier, and K. J. Hwang: Proc. 2020 Int. EOS/ESD Symp. Design and System (IEDS, 2021) 1–6. <u>https://ieeexplore.ieee.org/abstract/document/9468827</u>

- 24 C.-Y. Huang, Q.-K. Chen, J.-F. Chi, and T.-H. Huang: IEEE Trans. Device Mater. Reliab. 21 (2021) 64. <u>https://doi.org/10.1109/TDMR.2021.3050520</u>

- 25 Y. Wang, X. Jin, Y. Peng, J. Luo, J. Yang, Z. Zheng, L. Jiang, and Z. Zhong: IEEE J. Emerging Sel. Top. Power Electron 9 (2021) 994. <u>https://doi.org/10.1109/JESTPE.2019.2953469</u>

#### **About the Authors**

**Jhong-Yi Lai** is currently pursuing his master's degree with the Department of Electronic Engineering, National United University, Taiwan. His current projects focus on UHV power devices and ESD protection design.

**Shen-Li Chen** received his Ph.D. degree from National Tsing-Hua University, Taiwan, in 1992. He joined ERSO, ITRI, Taiwan in 1987, and worked with the research and development department responsible for the reliability analysis of submicron circuits. He then became a director of the Research and Development Division of AX and CG Electronics Corporation, where he focused on the design of I/O ESD/latch-up cells, especially those used in HV processes and DC-DC analog circuit design. In 2001, he joined the Department of Electronic Engineering, National United University, Taiwan, as an associate professor. In 2003, he was the chair of the Department of Electronic Engineering and Computer Science, National United University. Recently, he has continued to pursue his research interests in the modeling and characteristics of HV power devices and in high ESD/LU immunity designs in VLSI and power electronics.

**Zhi-Wei Liu** is currently studying for a master's degree in the Department of Electronic Engineering, National United University, Taiwan. His current projects focus on HV power devices and ESD protection design.

**Hung-Wei Chen** received his B.S. degree from the Department of Electronic Engineering, Feng Chia University in 1982, his M.S. degree in electrical engineering from University of Missouri-Columbia, MO, USA, in 1991, and his Ph.D. degree from the Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan in 2002. In 2002, he joined National United University (Taiwan) as an assistant professor and became an associate professor in 2008. His research interests include analog IC design, power electronics IC design, and the development of semiconductor oxide sensors.

**Hsun-Hsiang Chen** received his Ph.D. degree from National Tsing-Hua University, Taiwan, in 1998. In 2004, he joined National Changhua University of Education (Taiwan) as an assistant professor. Currently, his research interests include the design and analysis of microwave and millimeter-wave circuits, analog circuits, and electrostatic discharge protection circuits.

**Yi-Mu Lee** was born in Kaohsiung city, Taiwan. He received his bachelor degree in chemical engineering from National Cheng Kung University, Tainan, Taiwan, in 1993. He received his M.S. degree in chemical engineering and his Ph.D. degree in electrical and computer engineering from University of Missouri-Columbia and North Carolina State University, Raleigh, USA, in 1998 and 2003, respectively. In 2003, he joined the Department of Electronic Engineering, National United University, Taiwan. His research interests include solid-state electronics, thin-film processing and characterization, electrical measurements, and device reliability. Dr. Lee has published more than 30 peer-reviewed journal/conference papers and is currently serving as the chair of the Department of Electronic Engineering, National United University.