Sensors and Materials, Vol. 9, No. 6 (1997) 331–346 MYU Tokyo

S & M 0296

# **CMOS Micro Electro Mechanical Systems**

# Henry Baltes\*

Electrical and Computer Engineering, University of Waterloo, Waterloo, Ontario N2L 3G1, Canada

(Received May 11, 1996; accepted August 26, 1996)

Key words: CMOS, MEMS, micromachining, microtransducers, MEMS CAD

This introduction to the merging of MEMS and CMOS IC technology includes a summary of current technological approaches to CMOS MEMS, illustrations by selected CMOS MEMS microtransducer prototypes and an outline of the MEMS CAD tools, SOLIDIS and ICMAT.

## 1. Introduction

The term MEMS (micro electro mechanical systems) originally meant miniaturized electromechanical actuators, but now applies to a broad family of micromachined sensors, actuators and systems with coupled electrical, mechanical, radiant, thermal, magnetic and chemical effects. The acronyms IC MEMS, IMEMS (or iMEMS) and CMOS MEMS refer to silicon integrated MEMS based on integrated circuit (IC) technology combined with micromachining, thin film deposition or electrodeposition.<sup>(1-11)</sup>

For example, microsensors for thermal, mechanical and chemical measurands can be made by combining established CMOS IC technologies with CMOS-compatible additional processing steps specific to the sensor function. Preferably, such extra etching or deposition steps are performed by post-processing (also called post-CMOS), i.e., after completion of the regular IC process sequence. Pre-processing (pre-CMOS) and intermediate processing (intermediate CMOS) have also been demonstrated. Technological approaches to CMOS MEMS are summarized in section 2. Examples of post-CMOS microtransducer prototypes are demonstrated in section 3, whereas section 4 is dedicated to CMOS MEMS modeling and related materials characterization.

<sup>\*</sup>On leave from: Physical Electronics Laboratory, ETH Zurich, Switzerland.

## 2. CMOS MEMS Technologies

Here is a preliminary list of CMOS-compatible MEMS technologies:

- Bulk micromachining (wet or dry, isotropic or anisotropic, from wafer front or back).

- Surface micromachining (sacrificial oxide and/or metal or polysilicon).

- Micromachining before completion of IC process (pre-processing, pre-CMOS).

- Micromachining after completion of IC process (post-processing, post-CMOS).

- Micromachining inside or outside the IC foundry.

- Use of IC materials (monocrystalline silicon, polycrystalline silicon, oxide, nitride, metal, or gold bumps) for microstructures with electro-thermo-opto-mechanical functions.

- CMOS-compatible layer deposition, chemical-mechanical polishing, and wafer bonding.

Such techniques are currently being explored by researchers at Analog Devices, UC Berkeley, Carnegie-Mellon University, Cornell University, ETH Zurich, Fraunhofer Institut Dresden, Georgia Institute of Technology, University of Michigan, MIT, NIST, Sandia, Siemens, Stanford University, and several Canadian universities.

A summary of some of these developments is attempted in the following; it mainly draws from presentations at recent meetings such as IEDM, IEEE MEMS, Solid-State Sensor and Actuator Workshop, and IEEE ISCAS. Completeness is not attempted.

### 2.1 Post-CMOS micromachining

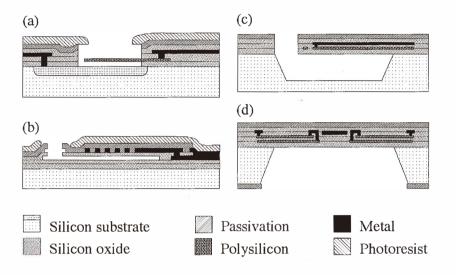

Four different ways to combine CMOS IC technology with micromachining are illustrated by the generic microtransducer cross sections shown in Fig. 1; these include two surface (a, b) and two bulk (c, d) micromachining techniques. The CMOS-compatible surface micromachining by sacrificial oxide etching (a) and sacrificial metal etching (b) is summarized as follows.

As indicated in Fig. 1(a), CMOS polysilicon microstructures can be formed by selective removal of the CMOS dielectric layers. This technique was demonstrated recently for a 0.8  $\mu$ m CMOS IC process of Siemens AG with a standard 0.35- $\mu$ m-thick gate polysilicon layer serving as the seismic mass for an accelerometer and a 0.6- $\mu$ m-thick field oxide serving as the sacrificial layer.<sup>(12,13)</sup> Buffered HF is used to release the seismic mass and the suspensions. Structural polysilicon with a thickness larger than that provided by the standard CMOS technology is feasible,<sup>(14)</sup> but requires interruption of the regular IC process (see section 2.3).

Figure 1(b) illustrates the CMOS-compatible sacrificial-metal surface micromachining technique.<sup>(2 - 5,15 - 17)</sup> The final structure is obtained by local removal of the lower CMOS metallization layer after completion of the IC process; this is achieved by including pad-like structures in the design layout that provide access to the metal layer to be removed. For the post-processing step, all exposed metal areas (contact pads) on the chip surface are protected with photoresist, except the access openings to the sacrificial layer. The selective removal of this metal by a commercial wet etchant results in a suspended membrane composed of the intermetal dielectric and the passivation layer, possibly with an upper metal layer sandwiched inbetween.

332

Fig. 1. Post-CMOS surface (a, b) and bulk (c, d) micromachining: sacrificial oxide etching for polysilicon microstructure (a), sacrificial metal etching for cavity structure (b), wafer front silicon etching for beam (c), and wafer back silicon etching for membrane (d).

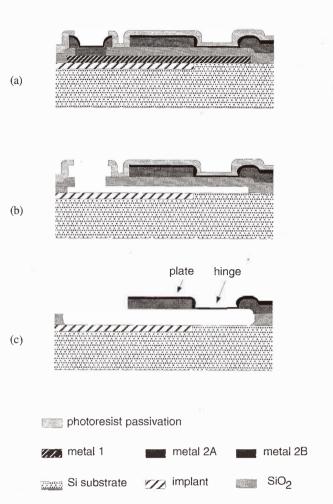

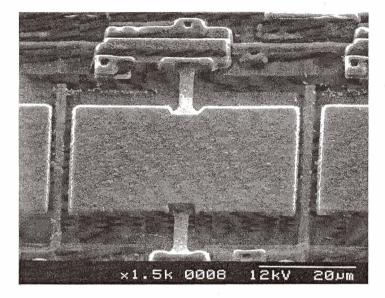

A combination of sacrificial metal and oxide etching allows fabrication of the CMOSbased electrostatic deflectable micromirror<sup>(18,19)</sup> shown in Figs. 2 and 3. The mirrors are made from the second metallization of the CMOS process deposited in two passes. Supercritical carbon-dioxide drying after the final rinse prevents the mirror from sticking to the substrate.

The two approaches to CMOS-compatible bulk micromachining illustrated in Fig. 1 are the removal of a portion of the silicon substrate from the front (c) or the back (d) of the wafer. Inherent features of CMOS technology and the etching properties of its (100) substrate allow the fabrication of open microstructures (beams or suspended membranes) by anisotropic silicon etching from the front of the wafer.<sup>(1-5)</sup> Possible etchants are EDP or TMAH, which preserve the integrity of the bonding pads. By design, the passivation layer serves as a mask. CMOS dielectric (oxide/nitride) beams or suspended membranes supporting thermal flow sensors<sup>(20,21)</sup> or thermally actuated micromirrors<sup>(22)</sup> can be made in this way. For thermal sensors, removal of part of the silicon substrate by bulk micromachining is crucial for thermal isolation. While EDP or TMAH front etching is useful for laboratory exploration of the feasibility of new microtransducer designs, this method may be less suitable for practical application.

Closed dielectric membranes (less sensitive to dust and humidity) are formed by etching from the back of the finished CMOS wafer.<sup>(1-5,23,24)</sup> An extra mask is required to define the membrane size. The preferred etchant is KOH. The front of the wafer is protected from the etchant by a mechanical chuck or etch protection layer. Here is an

Fig. 2. Post- and intermediate-CMOS fabrication of electrostatic deflectable micromirror using combined sacrificial metal and sacrificial oxide etch and double-pass metallization: after CMOS process (a), after sacrificial aluminum etch (b), and after oxide and passivation etch (c).

example for a specific list of process steps performed subsequent to the CMOS process sequence:

- Deposition of stress-compensated passivation nitride.

- Deposition of an etch protection layer on the wafer front.

- Isotropic etching of the wafer back to achieve good adhesive conditions.

- Deposition of the back nitride mask.

- Photolithography on the wafer back.

Fig. 3. SEM micrograph of electrostatically actuated CMOS-based micromirror.

- Etching in a 6 molar 95°C KOH solution.

- Dicing of the wafer.

The overall membrane yield after dicing is above 98%. Thanks to stress-controlled deposition of the silicon nitride passivation, low-stress membranes with less than 0.1  $\mu$ m buckling over an area as big as 720  $\mu$ m by 720  $\mu$ m are feasible.<sup>(2-5,23,24)</sup> The above bulk micromachining techniques produce CMOS dielectric beams or membranes with sandwiched metal and polysilicon thin-film structures used for a variety of thermal microtransducers such as thermoelectric infrared, vacuum, power and flow sensors, or thermally actuated micromirrors (see section 3).

Four alternative CMOS-compatible micromachining techniques have been demonstrated recently, two of which include the etching of silicon from the front of the wafer, the other two from the back:

(i) One front-etching technique uses the n-well as an electrochemical etch stop for EDP or TMAH and forms an n-well silicon beam suspended by dielectric hinges with electrical leads.<sup>(25)</sup> This thermally insulated n-well carries a CMOS circuit, which can be used for a temperature-regulated bandgap voltage reference<sup>(25)</sup> or a thermal vacuum sensor.<sup>(26)</sup>

(ii) The other front-etch technique produces laminated high-aspect-ratio microstructures starting from a finished triple-metal CMOS wafer post-processed by anisotropic oxide etching (to cut through the dielectric layers) followed by anisotropic and isotropic silicon etching to release a beam.<sup>(27)</sup>

(iii) A thermally isolated closed silicon membrane carrying thermocouples can be obtained using a SIMOX (Separation by IMplanted OXide) substrate.<sup>(28)</sup> The final silicon

membrane (thickness 200 nm) is separated from the bulk silicon by the implanted oxide layer (thickness 400 nm), which stops etching with TMAH from the wafer back.

(iv) Monocrystalline silicon membranes formed by the epitaxial silicon layer can be obtained by post-processing electrochemical etching with bipolar IC or BiCMOS technology on (100) silicon; here the epi-junction serves as etch stop for KOH etching of the silicon substrate from the back.<sup>(29)</sup> Similarly, the substrate can be partially removed by KOH anisotropic etching under the epi-layer in order to suppress the substrate current of magnetotransistors.<sup>(30)</sup>

Moreover, sacrificial polysilicon layer etching can be combined with bulk silicon etching in order to form cavities for integrated infrared sensors.<sup>(31)</sup>

### 2.2 Post-CMOS deposition

The substrate temperature during deposition must be kept below 400°C in order to preserve the CMOS metallization structures (consisting mainly of aluminum) of the preceding IC process. Permalloy (NiFe) layers can be deposited and patterned on finished CMOS wafers in order to form magnetic flux concentrators, enhancing the sensitivity of integrated silicon magnetic field sensors<sup>(32)</sup> or accelerometers.<sup>(33)</sup> The cost-effective deposition process uses standard ultraviolet (UV) lithography, a UV-sensitive resist such as photosensitive polyimide, and electrodeposition.<sup>(33)</sup>

The deposition of moisture adsorbing or absorbing thin films such as porous ceramics or organic polymers has been used for the demonstration of IC humidity sensors. Chemically selective polymers can be deposited on CMOS capacitive structures for hydrocarbon sensing.<sup>(34)</sup> On-chip capacitance measurement circuitry is crucial in view of the required femto Farad capacitance resolution.<sup>(35)</sup> A combination of post-processing bulk silicon micromachining and polyimide deposition and patterning has been used to demonstrate the feasibility of a CMOS integrated multisensor for HVAC (heating, ventilation, air conditioning), including a thermal flow sensor supported by a CMOS dielectric membrane and a capacitive moisture sensor.<sup>(36)</sup>

A post-processing sequence producing three additional aluminum layers separated by low-temperature oxide and an air gap has been developed for future application to finished CMOS wafers.<sup>(37)</sup> The additional structure serves as a variable capacitor by acting as a tuning element in voltage-controlled oscillators.

## 2.3 Other CMOS microtransducer technologies

Replacement of the usual CMOS metallization by tungsten with  $TiSi_2$  drain/source contact barriers allows post-CMOS micromachining and deposition with temperatures up to about  $800^{\circ}C$ .<sup>(38)</sup>

The BiMEMS technology of Analog Devices, Inc., combines the BiCMOS IC process with surface micromachined polysilicon structures for gyroscopes.<sup>(14,39)</sup> The IC process is interrupted before the last metallization; a spacer sacrificial oxide is deposited which allows the formation of 2- $\mu$ m-thick polysilcon mechanical structures. Finally, the aluminum metallization and the passivation of the IC process are completed.

A combined pre- and post-CMOS approach has been proposed where the polysilicon mechanical structures are embedded in an anisotropically etched trench below the surface

of the wafer.<sup>(40)</sup> Prior to the CMOS IC fabrication, this trench is refilled with oxide, chemical-mechanically polished, sealed with a nitride cap, and annealed to relieve stress in the structural polysilicon. After completion of the IC process, the nitride cap over the micromechanical layer is removed and the micromechanical structures are released by etching.

A different kind of merged MEMS CMOS process uses silicon wafer bonding to create a substrate that can be fitted into an existing IC fabrication line.<sup>(41)</sup> Front-end micromachining is used to form a sealed cavity substrate. Since the cavity is internal to the substrate, IC fabrication can proceed as usual, followed by low-temperature post-CMOS micromachining steps. Recently, the SCREAM (Single-Crystal-silicon Reactive Etching and Metallization) MEMS process has been redesigned to fit post-CMOS processing.<sup>(42)</sup> CMOS chips have been equipped with aluminum hinges to make contact with microhandling systems thanks to post-CMOS dry etching using XeF<sub>2</sub>.<sup>(43)</sup>

### 3. Post-CMOS Microsensor Prototypes

The post-CMOS technology outlined in sections 2.1 and 2.2 is illustrated by some prototypes designed, post-processed and characterized at the Physical Electronics Laboratory of ETH Zurich and CMOS-processed by its corporate partners. Sensors based on post-CMOS bulk micromachining (section 3.1), surface micromachining (section 3.2), deposition (section 3.3) and bulk micromachining combined with deposition (section 3.4) are reported.

#### 3.1 CMOS thermoelectric sensors

An infrared sensor<sup>(1-5,23,44)</sup> and an electrical power sensor<sup>(2-5,24)</sup> are presented as examples of microtransducers based on closed CMOS oxide/nitride membranes supporting n-polysilicon/p-polysilicon thermopiles, which are available in bidoped-poly CMOS IC technology.

The infrared sensor shown in Fig. 4 converts infrared radiation to a temperature increase by absorption in the CMOS passivation. Silicon dioxide/nitride absorbs in the wavelength range between 8  $\mu$ m and 14  $\mu$ m, which is useful for intrusion detection. The resulting temperature increase of a few mK on the sensor membrane is detected by the thermopile. Optimized devices with 1 mm<sup>2</sup> membrane reach a responsivity of about 100 V/W, a detectivity of about 5 × 10<sup>7</sup> cm/Hz/W, and a rise time of about 30 ms. Co-integration of an auto-zero operational amplifier<sup>(6-8)</sup> with a gain of 1,000 leads to a responsivity of 10<sup>5</sup> V/W.

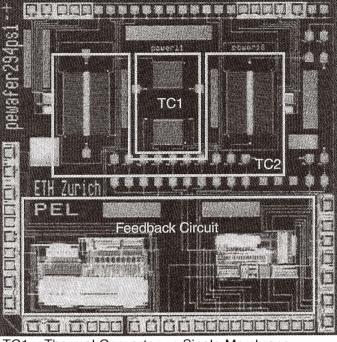

The AC power sensor or thermal converter detects the true root mean square value of an unknown ac signal in a wide frequency band. It is based on the square-law relationship between voltage and power in a 1000  $\Omega$  polysilicon heater resistor. The dissipated power is measured using bidoped polysilicon thermopiles with a sensitivity above 100 V/W. The nonlinearity at high power levels and the dependence on the ambient temperature are compensated for using a high dynamic range interface system.<sup>(6-8)</sup> It consists of two identical thermal converters operated at the same power level and a feedback circuit. The AC-DC voltage transfer difference is below 30 ppm between 1 kHz and 1 MHz. An

Fig. 4. Chip photo of two CMOS thermoelectric infrared sensors cointegrated with interface circuitry.

oversampled A/D converter embedded in the feedback loop provides a digital output proportional to the input power. The dynamic range is maximized by a variable bitstream amplitude adjusted according to the input signal and measured on-chip. Figure 5 shows an optical micrograph of an AC power sensor system chip with two pairs of thermal converters, one located on two separate membranes, the other on a single membrane.<sup>(24)</sup>

## 3.2 Thermal vacuum sensor

Thermal vacuum sensors can be based on the pressure-dependent heat transfer across an air gap separating a heat source from a heat sink. As shown in Fig. 1(b), the post-CMOS vacuum sensor<sup>(1-5,15-17)</sup> builds on the first metal layer (which is removed to form the gap), the intermetal dielectric, the second metal layer (which serves as heating resistor) and the passivation layer. The thermal power dissipated by the heater causes a temperature increase of the membrane, which depends on the thermal conductance provided by the (signal) heat transfer across the gap modulated by the air pressure and the (parasitic) heat flow through the sensor materials. The useful pressure range is  $10^2$  to  $10^6$  Pa in air.

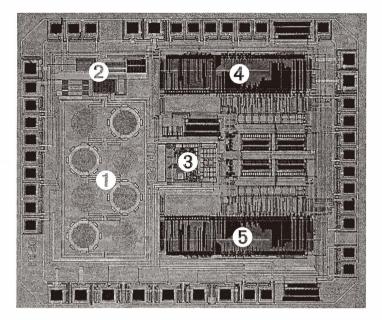

Figure 6 shows a chip photo of the vacuum sensor microsystem<sup>(17)</sup> with four surface micromachined pressure sensors (with gap) and four reference structures (without gap)

TC1 = Thermal Converter on Single Membrane TC2 = Thermal Converter on Separate Membranes

Fig. 5. Chip photo CMOS power microsensor with two pairs of thermal converters: one pair is located on two separate membranes, the other on a single membrane.

integrated with a front-end interface. The circuitry includes two incremental analog-todigital converters and a bandgap reference, and measures the pressure-dependent power required to maintain a constant temperature increase of the sensors. The chip (3.3 mm by 2.8 mm) was fabricated using a 2  $\mu$ m CMOS IC process followed by the sacrificial metal etching discussed in section 2.1.

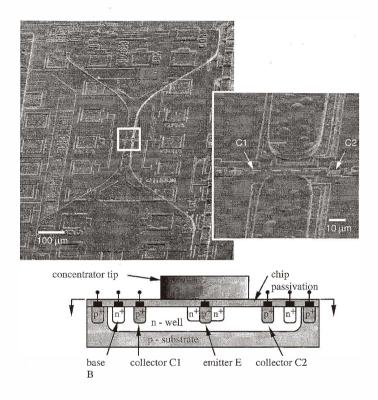

## 3.3 CMOS magnetotransistor with electroplated flux microconcentrator

As mentioned in section 2.2, thick ferromagnetic films can be deposited on passivated silicon wafers by electrodeposition.<sup>(33)</sup> This technique allows fabrication of the lateral magnetotransistor (LMT) with the permalloy flux microconcentrator<sup>(2,32)</sup> shown in Fig. 7. The microconcentrator consists of two funnel-shaped parts separated by an air gap in order to capture the external magnetic flux and guide it to the LMT located below the gap. For magnetic fields below 1 mT, the microconcentrator enhances the sensitivity by more than a factor of 20.

Fig. 6. Chip photo of CMOS microsystem consisting of four pressure and reference sensors (1) connected in series, front-end interface (2), bandgap reference (3), two incremental ADCs for current (4) and voltage (5) measurement.

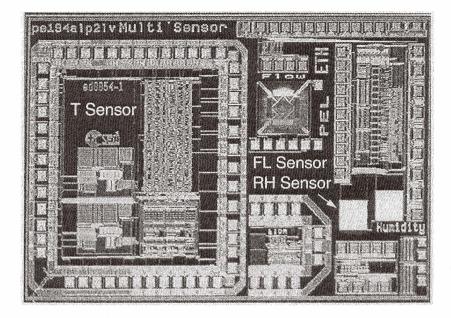

## 3.4 HVAC CMOS multisensor

Heating, ventilation and air conditioning (HVAC) require the control of air flow, humidity and temperature. Figure 8 shows a multi-sensor chip<sup>(36)</sup> with an air flow, a humidity and a temperature sensor connected, via a multiplexer, to a second-order sigma-delta analog-to-digital converter achieving 15-bit resolution.<sup>(6–8)</sup> No additional read-out circuitry is required. Prototypes (area 7 mm by 4 mm) have been fabricated using a commercial 2  $\mu$ m CMOS IC process combined with post-CMOS bulk micromachining and polyimide deposition.

The gas flow sensor consists of a CMOS dielectric membrane obtained by removing the bulk silicon locally under the thermal oxide. A heating resistor and p-polysilicon/n-polysilicon thermopiles are integrated in the membrane. The thermopiles measure the asymmetry of the temperature distribution occurring in the presence of flow. The humidity sensor consists of an interdigitated capacitor based on the CMOS metal layers; a polyimide cover is deposited after completion of the CMOS process. When the polyimide layer absorbs moisture from the environment, its permittivity, and thus the capacitance, increase. The chip includes an identical interdigitated structure, but without a polyimide cover, which serves as a reference capacitor.

Fig. 7. SEM micrograph and cross section of CMOS dual-collector magnetotransistor with integrated permalloy flux concentrator made by post-CMOS electroplating.

#### 4. Modeling and Characterization Tools

The design of CMOS MEMS is facilitated by the CAD tools SOLIDIS-a simulation toolbox for the numerical modeling of electrical, magnetic, thermal and mechanical effects and their couplings, and ICMAT-a data base of process-dependent electrical, magnetic, thermal and mechanical CMOS MEMS materials parameters measured with dedicated characterization microstructures, which may also serve as fabrication test structures.

## 4.1 SOLIDIS

SOLIDIS was developed at the Physical Electronics Laboratory of ETH Zurich <sup>(9–11,45–47)</sup> for efficient and accurate simulation of realistic three-dimensional microstructures performed by the microtransducer designers. The benefits are fast and inexpensive numerical simulation (faster and less expensive than prototyping) and the clarification of topographically complex scenarios.

Fig. 8. Chip photo of CMOS HVAC multi-sensor for temperature (T), air flow (FL), and relative humidity (RH).

Coupled physical effects are basic to many IC microtransducers. The finite element program system SOLIDIS reflects this fact by providing analytical facilities for different physical effects in both individual and coupled form. The theoretical basis for the coupling is an Onsager scheme for the case of irreversible effects, and a Nye scheme for the case of reversible effects. Both of these have similar mathematical structure and only contain operators derived from conservation and constitutive laws. The variables and operators are discretized using the finite element method, and the discrete system of equations is automatically partitioned to reflect the different coupling requirements of various zones in a typical microstructure.

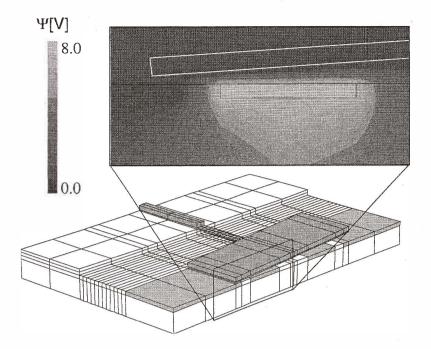

The present program couples electrostatics, thermostatics and elastostatics. These three effects are important not only in MEMS devices, but also for any other micromechanical structure producing heat, as well as for packaged microsystems. Crucial to the microtransducer designer are the available boundary conditions, interface conditions and nonlinear physical model equations. Accuracy is attained by automatic adaptation of the finite element mesh according to a refinement estimator, together with the ability to solve for very large meshes (about 100,000 finite elements) on engineering workstations in reasonable time. As an example, the simulation<sup>(11)</sup> of the fabricated electrostatically actuated integrated micromirror in Fig. 3 is shown in Fig. 9.

Fig. 9. Coupled simulation of deflection and elec**w**ostatic potential distribution in a cross section of the micromirror shown in Fig 3.

#### 4.2 ICMAT

The knowledge of precise values of material properties is a prerequisite of design and simulation of microtransducers. This is particularly true for microstructures produced using commercial CMOS processes. Many more physical properties than those routinely monitored in IC fabrication play a role and must be determined for each CMOS layer:

- Thermal properties such as thermal conductivity and heat capacity.

- Electronic transport properties such as thermopower, carrier density n (or p) and piezoresistance of polysilicon.

- Mechanical properties such as Young's modulus, Poisson's ratio and stress.

A systematic characterization of these thin film properties and the variation with different vendors, processes, and batches is required in view of their process-dependence.<sup>(4,5,10,48-50)</sup>

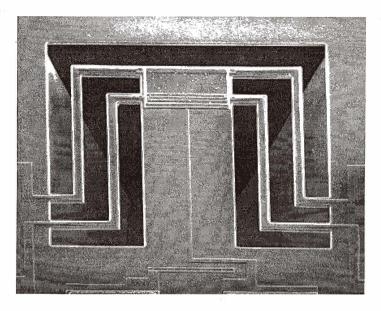

These measurements are conducted using dedicated CMOS-compatible characterization microstructures, an example of which is shown in Fig. 10. Such test structures are produced by appropriate design layout and post-CMOS technology similar to the post-CMOS microtransducer technology described in section 2.1. The thermal properties of oxides are only slightly different from the bulk values. Metal layers have thermal conductivities reduced by typically 30% from bulk. The thermal properties of polycrystalline silicon deviate strongly from those of monocrystalline silicon.<sup>(48–50)</sup>

Fig. 10. SEM micrograph of characterization microstructure, with polysilicon heating resistor and thermistor at the tip, used to determine the Seebeck coefficient of a CMOS polysilicon layer.

## 5. Outlook

From the technological feasibility viewpoint, the most promising technologies for CMOS MEMS products are those requiring minimal post-processing of finished CMOS wafers. Simple intermediate processing using conventional IC fabrication equipment with the wafers remaining in the CMOS line is another likely candidate. While industrial CMOS MEMS chip manufacturing seems to be only a couple of years away, the packaging of microtransducers is more demanding. Strong efforts must be made to develop micro-transducer packaging techniques, case by case, until they become established.

By exploiting the predicted progress of semiconductor IC capabilities, the part that makes the sensor smart will increase at a phenomenal rate. By the year 2010 we will probably have not only a pressure sensor with integrated microcontroller, but also the HVAC sensor, the viscosimeter and even the taste sensor, artificial nose and atomic force microscope on a chip. Thus the trend to merge MEMS and IC technologies will continue. The author believes that the potential for joint university-industry IC MEMS development is overwhelming.

#### Acknowledgments

It is my pleasure to thank my colleagues Mark Allen (Georgia Institute of Technology), Greg Kovacs (Center for Integrated Systems, Stanford University), and Arokia Nathan (University of Waterloo) for stimulating discussions of microtransducer technology and generous hospitality during the summer of 1996. I am grateful to the staff of the Physical Electronics Laboratory at ETH Zurich, notably Johannes Bühler, Joerg Funk, Andreas Häberli, Dominik Jaeggi, Jan Korvink, Piero Malcovati, Felix Mayer, Oliver Paul, Niklaus Schneeberger, Michael Schneider, F.-P. Steiner and Martin von Arx, whose publications are quoted in this paper. The excellent services of the silicon vendors Austria Mikro Systeme (Volker Kempe), ATMEL ES2 (Philippe Sagnol), DIMES (Pasqualina Sarro) and EM Microelectronic Marin (Elko Doering) are gratefully aclenowledged as well as the financial support of the Swiss Confederation through the research programs ESPRIT, KTI (formerly KWF), LESIT and MINAST.

#### References

- 1 H. Baltes: Elektrotechnik und Informationstechnik **112** (1995) 488.

- 2 H. Baltes: Sensors and Actuators A 56 (1996) 179.

- 3 H. Baltes, O. Paul, J. G. Korvink, M. Schneider, J. Bühler, N. Schneeberger, D. Jaeggi, P. Malcovati, M. Hornung, A. Häberli, M. von Arx and J. Funk: IEDM Technical Digest, IEEE (1996) 521.

- 4 H. Baltes and O. Paul: Sensors and Materials 8 (1996) 409.

- 5 H. Baltes, O. Paul and D. Jaeggi: Sensors Update 1 (1996) 121.

- 6 H. Baltes, A. Häberli, P. Malcovati and F. Maloberti: IEEE ISCAS 4 (1996) 380.

- 7 P. Malcovati: CMOS Thermoelectric Sensor Interfaces, Ph. D. Thesis No. 11424, ETH Zurich 1996.

- 8 P. Malcovati, F. Maloberti and H. Baltes: Progress in Microsensor Interfaces, Sensors Update 1 (1996) 143.

- 9 J. G. Korvink and H. Baltes: Sensors Update 2 (1996) 181.

- 10 H. Baltes, J. G. Korvink and O. Paul: Simulation of Semiconductor Devices and Processes 6 (1995) 1.

- 11 J. Funk: Modelling and Simulation of IMEMS, Ph. D. Thesis No. 11378, ETH Zurich (1995).

- 12 M. Biebl, T. Scheiter, C. Hierold, H. v. Philipsborn and H. Klose: Sensors and Actuators A 46 -47 (1995) 593.

- 13 C. Hierold, A. Hildebrandt, U. N\u00e4her, T. Scheiter, B. Mensching and M. Steger, R. Tielert: Proc. IEEE MEMS (1996) p. 174.

- 14 W. Kuehnel and S. Sherman: Sensors and Actuators A 45 (1994) 7.

- 15 O. Paul, A. Häberli, P. Malcovati and H. Baltes: IEDM Technical Digest, IEEE (1994) p. 131.

- 16 O. Paul and H. Baltes: Sensors and Actuators A 46-47 (1995) 143.

- 17 A. Häberli, O. Paul, M. Faccio, F. Maloberti and H. Baltes: Proc. IEEE ISCAS (1996) 377.

- 18 J. Bühler, F.-P. Steiner and H. Baltes: J. Micromech. and Microeng 7 (1997) R1.

- 19 J. Bühler, J. Funk, J. G. Korvink, F.-P. Steiner, P. M. Sarro and H. Baltes: IEEE J. MEMS 7 (1996) 126.

- 20 F. Mayer, G. Salis, O. Paul and H. Baltes: Proc. IEEE MEMS (1996) p. 116.

- 21 N. R. Swart and A. Nathan: IEDM Technical Digest, IEEE (1994) p. 135.

- 22 J. Bühler, J. Funk, O. Paul, F.-P. Steiner and H. Baltes: Sensors and Actuators A 46-47 (1995) 572.

- 23 R. Lenggenhager, D. Jaeggi, P. Malcovati, H. Duran, H. Baltes and E. Doering: IEDM Technical Digest, IEEE (1994) 531.

- 24 D. Jaeggi: Thermal Converters by CMOS Technology, Ph. D. Thesis No. 11567, ETH Zurich 1996.

- 25 R. J. Reay, E. H. Klassen and G. T. A. Kovacs: IEEE J. Solid-State Circuits 30 (1995) 1374.

- 26 E. H. Klaassen and G. T. A. Kovacs: Solid State Sensor and Actuator Workshop Technical Digest, TRF (1996) 249.

- 27 G. K. Fedder, S. Santhanam, M. L. Reed, S. C. Eagle, D. F. Guillou, M. S.-C. Lu and L. R. Carley: Proc. IEEE MEMS (1995) p. 13.

- 28 M. Müller, R. Gottfried-Gottfried, H. Kück and W. Mokwa: Transducers 95 Digest of Technical Papers 2 (1995) 640.

- 29 M. Hornung, R. Frey, O. Brand, H. Baltes and C. Hafner: Proc. IEEE MEMS (1995) p. 151.

- 30 R. Castagnetti, M. Schneider and H. Baltes: Sensors and Actuators A 46-47 (1995) 280.

- 31 S. Sugiyama, O. Tabata, K. Shimaoka, R. Asahi: IEDM Technical Digest, IEEE (1994) p. 135.

- 32 M. Schneider, R. Castagnetti, M. G. Allen and H. Baltes: Proc. IEEE MEMS (1995) p. 151.

- 33 Y. Konaka and M. G. Allen: Proc. IEEE MEMS (1996) p. 168.

- 34 C. Cornila, A. Hierlemann, R. Lenggenhager, P. Malcovati, H. Baltes, G. Noetzel, U. Weimar and W. Göpel: Sensors and Actuators B 24–25 (1995) 357.

- 35 H. Baltes and C. Azeredo Leme: Sensors 8 (1995) 52.

- 36 P. Malcovati, A. Häberli, F. Mayer, O. Paul, F. Maloberti and H. Baltes: Symposium on VLSI Circuits Digest of Technical Papers (1995) 45.

- 37 D. J. Young and B. E. Boser: Proc. IEEE MEMS (1996) p. 86.

- 38 C. T.-C. Nguyen and R. Howe: IEDM Technical Digest, IEEE (1993) p. 199.

- 39 W. A. Clark, R. T. Howe and R. Horowitz: Solid State Sensor and Actuator Workshop Technical Digest, TRF (1996) p. 283.

- 40 J. H. Smith, S. Montague, J. J. Sniegowski, J. R. Murray and P. J. McWhorter: IEDM Technical Digest, IEEE (1995) p. 609.

- 41 L. Parameswaran, C. Hsu and M. A. Schmidt: IEDM Technical Digest, IEEE (1995) p. 613.

- 42 K. A. Shaw and N. C. MacDonald: Proc. IEEE MEMS (1996) p. 44.

- 43 G. Lin, K. S. Pister and K. P. Roos: Proc. IEEE MEMS (1996) p. 150.

- 44 P. Malcovati, C. Azeredo Leme, R. Lenggenhager, F. Maloberti and H. Baltes: IEEE Trans. Instrumentation and Measurement 44 (1995) 795.

- 45 J. G. Korvink, J. Funk and H. Baltes: Sensors and Materials 6 (1994) 235.

- 46 J. Funk, J. Bühler, J. G. Korvink and H. Baltes: Sensors and Actuators A 46-47 (1995) 632.

- 47 J. Funk, J. G. Korvink, M. Bächtold and H. Baltes: Proc. IEEE MEMS (1996) p. 133.

- 48 M. Von Arx, O. Paul and H. Baltes: Sensors and Actuators A 46–47 (1995) 428.

- 49 O. Paul, M. von Arx and H. Baltes: Semiconductor Characterization Present Status and Future Needs, ed. W. M. Bullis, D. G. Seiler and A. C. Diebold, American Institute of Physics (1996) p. 197.

- 50 M. von Arx, O. Paul and H. Baltes: Proceedings of the 1996 International Conference on Microelectronic Test Structures, Trento, Italy **9** (1996) p. 117.