Young Researcher Paper Award 2025

🥇Winners

🥇Winners

Print: ISSN 0914-4935

Online: ISSN 2435-0869

Sensors and Materials

is an international peer-reviewed open access journal to provide a forum for researchers working in multidisciplinary fields of sensing technology.

Online: ISSN 2435-0869

Sensors and Materials

is an international peer-reviewed open access journal to provide a forum for researchers working in multidisciplinary fields of sensing technology.

Tweets by Journal_SandM

Sensors and Materials

is covered by Science Citation Index Expanded (Clarivate Analytics), Scopus (Elsevier), and other databases.

Instructions to authors

English 日本語

Instructions for manuscript preparation

English 日本語

Template

English

Publisher

MYU K.K.

Sensors and Materials

1-23-3-303 Sendagi,

Bunkyo-ku, Tokyo 113-0022, Japan

Tel: 81-3-3827-8549

Fax: 81-3-3827-8547

MYU Research, a scientific publisher, seeks a native English-speaking proofreader with a scientific background. B.Sc. or higher degree is desirable. In-office position; work hours negotiable. Call 03-3827-8549 for further information.

MYU Research

(proofreading and recording)

MYU K.K.

(translation service)

The Art of Writing Scientific Papers

(How to write scientific papers)

(Japanese Only)

is covered by Science Citation Index Expanded (Clarivate Analytics), Scopus (Elsevier), and other databases.

Instructions to authors

English 日本語

Instructions for manuscript preparation

English 日本語

Template

English

Publisher

MYU K.K.

Sensors and Materials

1-23-3-303 Sendagi,

Bunkyo-ku, Tokyo 113-0022, Japan

Tel: 81-3-3827-8549

Fax: 81-3-3827-8547

MYU Research, a scientific publisher, seeks a native English-speaking proofreader with a scientific background. B.Sc. or higher degree is desirable. In-office position; work hours negotiable. Call 03-3827-8549 for further information.

MYU Research

(proofreading and recording)

MYU K.K.

(translation service)

The Art of Writing Scientific Papers

(How to write scientific papers)

(Japanese Only)

Sensors and Materials, Volume 37, Number 12(3) (2025)

Copyright(C) MYU K.K.

Copyright(C) MYU K.K.

|

pp. 5597-5608

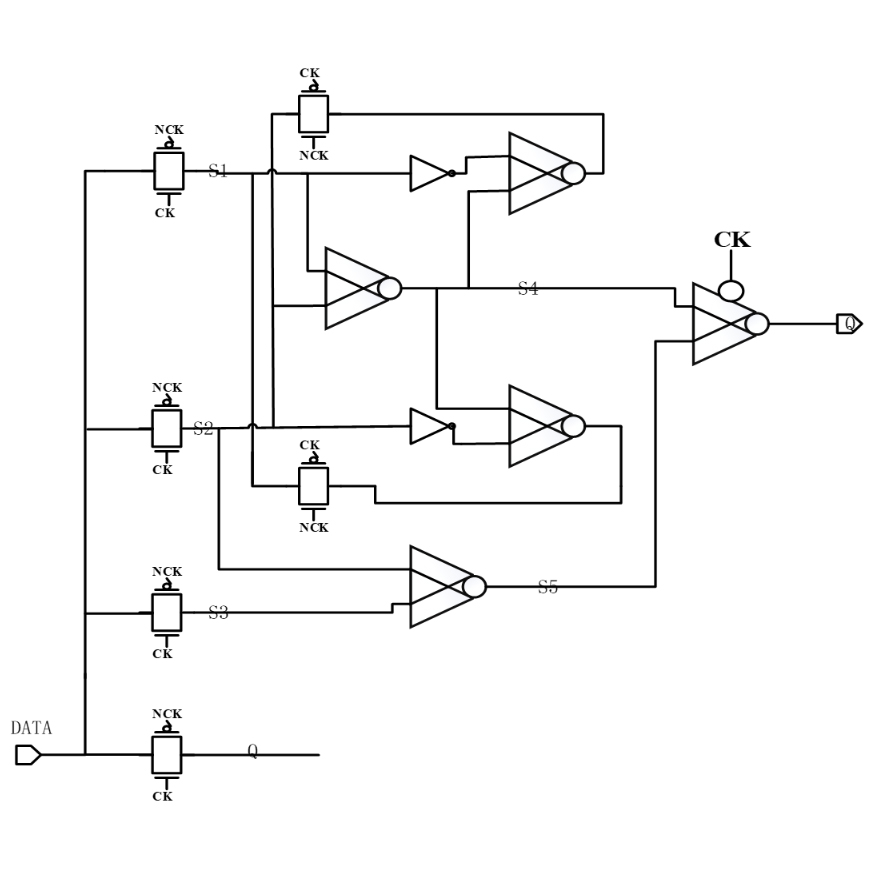

S&M4266 Research paper https://doi.org/10.18494/SAM5783 Published: December 26, 2025 Novel Design of Low-power Double Node Upset Tolerant Latch Cell [PDF] Huixiang Huang, Chih-Cheng Chen, Tao Huang, Zijian Cui, Jieliang Gu, and Jie Luo (Received June 5, 2025; Accepted December 5, 2025) Keywords: double node upset (DNU), radiation hardened by design (RHBD), C-elements, low power

To enhance the reliability of sensor interfaces and signal-processing circuits operating in radiation environments, a novel low-power double node upset (DNU)-tolerant latch, termed the low-power double-node upset tolerant (LDUT) latch, is proposed and implemented in this work. The design employs a redundant architecture based on C-elements (CE) and a self-recovery cell (SRC) module, achieving full DNU self-recovery capability through a clock-controlled feedback loop that enhances circuit robustness for sensor-related electronic systems. Simulation results under the Taiwan Semiconductor Manufacturing Company (TSMC) 65 nm CMOS technology demonstrate that the LDUT latch significantly outperforms existing designs in key performance metrics. Dynamic power consumption is reduced to 0.77 μW, representing an improvement of 25.08% compared with the high-performance, low-cost, and DNU-tolerant latch (HLDTL) and 87.3% compared with the DNU-resilient latch (DNURL) design. Further process-voltage–temperature (PVT) analysis shows that the LDUT latch also provides low sensitivity to temperature variations, making it suitable for radiation-hardened sensor applications and high-reliability integrated circuits.

Corresponding author: Chih-Cheng Chen  This work is licensed under a Creative Commons Attribution 4.0 International License. Cite this article Huixiang Huang, Chih-Cheng Chen, Tao Huang, Zijian Cui, Jieliang Gu, and Jie Luo, Novel Design of Low-power Double Node Upset Tolerant Latch Cell, Sens. Mater., Vol. 37, No. 12, 2025, p. 5597-5608. |

Forthcoming Regular Issues

Forthcoming Special Issues

Special Issue on Signal Collection, Processing, and System Integration in Automation Applications 2026

Guest editor, Hsiung-Cheng Lin (National Chin-Yi University of Technology), Ming-Te Chen (National Chin-Yi University of Technology), and Chin-Yi Cheng (National Yunlin University of Science and Technology)

Call for paper

Special Issue on Advanced GeoAI for Smart Cities: Novel Data Modeling with Multi-source Sensor Data

Guest editor, Prof. Changfeng Jing (China University of Geosciences Beijing)

Call for paper

Special Issue on Advanced Sensor Application Development

Guest editor, Shih-Chen Shi (National Cheng Kung University) and Tao-Hsing Chen (National Kaohsiung University of Science and Technology)

Call for paper

Special Issue on Mobile Computing and Ubiquitous Networking for Smart Society

Guest editor, Akira Uchiyama (The University of Osaka) and Jaehoon Paul Jeong (Sungkyunkwan University)

Call for paper

Special Issue on Advanced Materials and Technologies for Sensor and Artificial- Intelligence-of-Things Applications (Selected Papers from ICASI 2026)

Guest editor, Sheng-Joue Young (National Yunlin University of Science and Technology)

Conference website

Call for paper

Special Issue on Biosensing Devices

Guest editor, Kiyotaka Sasagawa (Nara Institute of Science and Technology)

Call for paper

-

For more information of Special Issues (click here)

-

Special Issue on Innovations in Multimodal Sensing for Intelligent Devices, Systems, and Applications (submission closed)

- Accepted papers (click here)

- Implementation of Deep-Neural-Network–based Unmanned Aerial Vehicle Platform for Fire Smoke Response: Wildfire Smoke Description Experiments

Tae-Hwan Kim, Eun-Su Seo, and Se-Hyu Choi - User-centric Real-time System for Building Disaster Alerts

Tae-Hwan Kim, Eun-Su Seo, and Se-Hyu Choi

- Implementation of Deep-Neural-Network–based Unmanned Aerial Vehicle Platform for Fire Smoke Response: Wildfire Smoke Description Experiments

- Accepted papers (click here)

- High-precision Autonomous Driving Map Quality Inspection Indicator System and Evaluation Method

Chengcheng Li, Ming Dong, Hongli Li, Xunwen Yu, Yongxuan Liu, and Chong Zhang - Surface Albedo in Different Land Cover Types in Northeast China

Tao Pan, Fu Li, Yucheng Tao, Lijuan Zhang, and Xiaoyan Jiang

- High-precision Autonomous Driving Map Quality Inspection Indicator System and Evaluation Method

- Accepted papers (click here)

- Voltage Reflex and Equalization Charger for Series-connected Batteries

Cheng-Tao Tsai and Jia-Wei Lin

- Voltage Reflex and Equalization Charger for Series-connected Batteries

- Accepted papers (click here)

- Design and Development of a Fuzzy-logic-based Long-range Aquaculture System

Sheng-Tao Chen and Tai-I Chou

- Design and Development of a Fuzzy-logic-based Long-range Aquaculture System

Guest editor, Jiahui Yu (Research scientist, Zhejiang University), Kairu Li (Professor, Shenyang University of Technology), Yinfeng Fang (Professor, Hangzhou Dianzi University), Chin Wei Hong (Professor, Tokyo Metropolitan University), Zhiqiang Zhang (Professor, University of Leeds)

Call for paper

Special Issue on Novel Sensors, Materials, and Related Technologies on Artificial Intelligence of Things Applications

Guest editor, Teen-Hang Meen (National Formosa University), Wenbing Zhao (Cleveland State University), and Cheng-Fu Yang (National University of Kaohsiung)

Call for paper

Special Issue on Low-altitude Economy: Technologies, Infrastructure, and Applications

Guest editor, He Huang and Junxing Yang (Beijing University of Civil Engineering and Architecture)

Call for paper

Special Issue on Multisource Sensors for Geographic Spatiotemporal Analysis and Social Sensing Technology Part 5

Guest editor, Prof. Bogang Yang (Beijing Institute of Surveying and Mapping) and Prof. Xiang Lei Liu (Beijing University of Civil Engineering and Architecture)

Special Issue on Materials, Devices, Circuits, and Analytical Methods for Various Sensors (Selected Papers from ICSEVEN 2025)

Guest editor, Chien-Jung Huang (National University of Kaohsiung), Mu-Chun Wang (Minghsin University of Science and Technology), Shih-Hung Lin (Chung Shan Medical University), Ja-Hao Chen (Feng Chia University)

Conference website

Call for paper

Special Issue on Advances in Sensors and Computational Intelligence for Industrial Applications

Guest editor, Chih-Hsien Hsia (National Ilan University)

Call for paper

Special Issue on AI-driven Sustainable Sensor Materials, Processes, and Circular Economy Applications

Guest editor, Shih-Chen Shi (National Cheng Kung University) and Tao-Hsing Chen (National Kaohsiung University of Science and Technology)

Call for paper

Special Issue on Intelligent Sensing and AI-driven Optimization for Sustainable Smart Manufacturing

Guest editor, Cheng-Chi Wang (National Sun Yat-sen University)

Call for paper

- Accepted papers (click here)

Copyright(C) MYU K.K. All Rights Reserved.